Andreas Berheide - Fotolia

Diese vier Storage-Trends für 2021 sollten Sie kennen

IT-Abteilungen, die in diesem Jahr die Effizienz und Performance ihrer Speichersysteme steigern wollen oder müssen, sollten diese vier wichtigsten Trends im Auge behalten.

Im Jahr 2020 gab es erhebliche Veränderungen im Storage-Ökosystem. Und 2021 wird sich dieser Trend fortsetzen.

Im Jahr 2020 sahen Speicheradministratoren Fortschritte und Updates in Bezug auf Storage Class Memory (SCM), 3D Quad-Level Cell (QLC)-Laufwerke, Cloud-Speicher, Kubernetes Persistent Storage und maschinelles Lernen.

In diesem Jahr gibt es mehrere aufkommende Speichertechnologien, die reifen und ihren Weg in die Unternehmen finden:

- PCIe Gen 4 und Gen 5

- Compute Express Link (CXL) 2.0

- Switchless Interconnect

- Data Processing Units (DPUs)

Auch wenn einige dieser Technologien nicht bahnbrechend erscheinen mögen, werden sie einen tiefgreifenden Einfluss auf die Speicherleistung haben. Die meisten werden wahrscheinlich in Servern von Anbietern wie Dell Technologies, HPE, Cisco und Supermicro erscheinen, bevor sie in Speichersystemen zum Einsatz kommen. Software-definierter Speicher (SDS) ist wahrscheinlich der erste Speichertyp, der sich diese Vorteile zunutze macht.

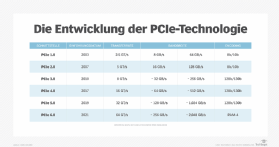

PCIe Gen 4 und Gen 5

PCIe Gen 4 liefert doppelt so viel Bandbreite pro Lane wie Gen 3, und Gen 5 liefert doppelt so viel wie Gen 4. Dies ist entscheidend, um ein großes externes und internes Interconnect-Bandbreitenproblem zu beseitigen. Ein Gen 3-PCIe-Steckplatz bietet einen Gesamtdurchsatz von circa 32 GBit/s, das heißt fast 256 Gbit/s (siehe Tabelle unten). Das reicht nicht für mehrere Netzwerkkarten (NICs) oder Adapter mit 200 Gbit/s, geschweige denn für Interconnects mit 400 Gbit/s; es wird zu einem Performance-Engpass.

Die gute Nachricht ist, dass Gen 4 einen Gesamtdurchsatz von etwa 64 GBit/s oder etwa 512 GBit/s liefert, was für mehrere 200-GBit/s-Ports mehr als ausreichend ist. Gen 5 verdoppelt diesen Wert noch einmal auf fast 128 GBit/s beziehungsweise etwa 1.024 GBit/s und löst damit das Problem mehrerer 400-Gbit/s-Interconnects.

Intel sagt, dass seine Prozessoren sowohl Gen 4 als auch Gen 5 im Jahr 2021 unterstützen werden. AMD unterstützt Gen 4, will Gen 5 ab 2022 unterstützen. Da die meisten Storage-Controller auf Intel und AMD basieren, ist zu erwarten, dass Storage-Systeme ab 2021 PCIe Gen 4 und Gen 5 unterstützen. Bis 2022 sollte die Unterstützung von Gen 5 zum Standard werden.

Compute Express Link – CXL 2.0

Die Unterstützung von PCIe Gen 5 ist wichtig wegen der neuesten Version der offenen Standardschnittstelle CXL 2.0. CXL ist ein CPU-to-Device-Interconnect-Protokoll auf PCIe, das auf Hochleistungs-Workloads abzielt. Es nutzt speziell die Vorteile der PCIe Gen 5-Spezifikation und ermöglicht es alternativen Protokollen, den PCIe Physical Layer zu nutzen.

Sobald CXL-basierte Beschleuniger in einen PCIe x16 (16-Lane)-Steckplatz eingesteckt sind, verhandelt es mit dem Host-Prozessorport über PCIe 5.0-Übertragungsraten von 32 Gigatransfers pro Sekunde (GT/s). Wenn beide Seiten CXL 2.0 unterstützen, verwenden sie CXL-Transaktionsprotokolle, die effizienter sind und geringere Latenz haben. Wenn eine oder beide Seiten CXL 2.0 nicht unterstützen, arbeiten sie als Standard-PCIe-Geräte. Die Übertragungsgeschwindigkeiten betragen bis zu 64 GB/s bidirektional über eine 16-Lane-Verbindung.

Diese Details haben einen enormen potenziellen Einfluss auf die Leistung von Speichersystemen und SDS. CXL verbessert die Leistung gegenüber PCIe mit den drei Transaktionsprotokollen CXL.io, CXL.cache und CXL.memory deutlich und wesentlich. CXL.io ist fast nicht von PCI Express 5.0 zu unterscheiden. CXL.io wird für Geräteerkennung, Konfiguration, Registerzugriff, Interrupts, Virtualisierung und Bulk-Direct Memory Access (DMA) verwendet. Dies ist das Hauptprotokoll. CXL.cache und CXL.memory sind optional. CXL.cache befähigt Beschleuniger, Systemhauptspeicher zu cachen, um CXL-Kohärenz zu ermöglichen. CXL.memory ermöglicht Host-Prozessoren den direkten Zugriff auf den mit dem Beschleuniger verbundenen Memory. Die CPU, GPU oder TPU kann dieses an den Beschleuniger angeschlossene Memory als einen zusätzlichen Adressraum betrachten. Dadurch werden viele Ineffizienzen und Latenzzeiten eliminiert.

Obwohl die Technologie in erster Linie auf heterogenes Computing abzielt, gibt es mit NVMe-SSDs, NVMe-SCM, Scale-out-Speichersystemen und SDS auch ein interessantes Speicherspiel. Die Kohärenz zwischen dem CPU-Speicherbereich und dem Memory in angeschlossenen Geräten eliminiert die hin und her gehenden DMA-Operationen, indem direkt in das Speichersystem des anderen Geräts gelesen und geschrieben wird.

Große Anbieter, darunter Intel, AMD und Nvidia, unterstützen CXL 2.0, was für die Marktakzeptanz dieser aufstrebenden Speichertechnologie spricht. Erwarten Sie, dass die ersten CXL 2.0-Systeme und -Laufwerke irgendwann in der zweiten Hälfte des Jahres 2021 erscheinen werden.

Switchless Interconnect

Switchless Interconnect löst ein großes Speicherproblem. Wenn die Skalierungsanforderungen steigen, werden Switchesweniger effizient, fügen mehr Latenz hinzu und erhöhen die Kosten.

Switchless Interconnect führt ein eigenes Routing durch. Es begrenzt Hops und Latenz und reduziert die Anforderungen an Stromversorgung, Kühlung, Rack-Platz, Kabel und Transceiver. Es kann eine Dragonfly-Konfiguration anstelle eines Fat Tree verwendet werden. Dies vereinfacht die großen Konfigurationen, die in High-Performance-Computing-Umgebungen erforderlich sind. Der Anbieter, der Switchless Interconnect liefert, hat Jahre in die Entwicklung investiert. Obwohl sich der Anbieter noch im Stealth-Modus befindet, ist zu erwarten, dass diese Technologie in der zweiten Hälfte des Jahres 2021 in Speichersystemen und SDS zu sehen sein wird.

Data Processing Units – DPUs

DPUs (Data Processing Units oder Datenverarbeitungseinheiten) sind eine weitere aufkommende Speichertechnologie, die man 2021 im Auge behalten sollte. Derzeit gibt es zwei auf dem Markt: eine von Nvidia/Mellanox und eine von Fungible.

Die DPU von Nvidia/Mellanox konzentriert sich auf die Netzwerk-Offloads. Die DPU von Nvidia/Mellanox konzentriert sich auf den Offload von Netzwerkprotokollen, wie RDMA, NVMe/JBOF, Storage Space Direct (S2D mit RDMA), Lustre RDMA, NFS RDMA, NVMe-oF (RDMA over Converged Ethernet, InfiniBand, TCP/IP), Open vSwitch Kernel Datapath Offload, Network Packet Shaping, Nvidia GPUDirect und User Datagram Protocol Offload.

Die Nvidia/Mellanox DPU zielt darauf ab, die Kommunikation zwischen Initiatoren und Zielen zu beschleunigen. Der Nvidia/Mellanox Connect-X NIC/Adapter zeichnet sich im Markt durch seine hohe Performance aus, insbesondere im Storage-Bereich. Das wird wahrscheinlich auch 2021 so bleiben. Allerdings ist Fungible ein starker Konkurrent.

Es gibt zwei verschiedene DPUs von Fungible. Die eine ist ein Initiator, der in Servern läuft. Die andere ist speziell ein Storage-Target mit bis zu vierfacher Bandbreite bei 800 Gbps. Die Fungible DPU ist so konzipiert, dass sie alle Infrastrukturdienste von x86-Prozessoren auslagert. Sie arbeitet sowohl mit PCIe Gen 3 als auch Gen 4. Sie verfügt über integrierte Ver-/Entschlüsselung, Kompression/Dekompression und Programmierbarkeit. Sie unterstützt NVMe-oF, NVMe over TCP und, als Besonderheit, Fungible TrueFabric. TrueFabric reduziert die Latenz weiter und garantiert nicht mehr als drei Hops, egal wie groß die Anzahl der Initiatoren, Switches und Ziele ist. TrueFabric erfordert sowohl Fungible-Initiatoren als auch Fungible-Storage-Targets, wobei letztere mit Nvidia/Mellanox-Initiatoren kompatibel sind.

Erwarten Sie, dass in der zweiten Hälfte des Jahres 2021 weitere Speichersysteme auf Basis der Fungible DPU auf dem Markt erscheinen.