stefanocar_75 - Fotolia

Die Vorteile der Charge-Trap-Technologie für 3D NAND Flash

Flash-Drive-Zellen, die auf der Charge-Trap-Technologie basieren, haben mehrere Vorteile gegenüber älteren Floating-Gate-Zellen. Es gibt jedoch potenzielle Zuverlässigkeitsprobleme.

In den letzten zehn Jahren hat die Speicherindustrie einen stillen Wandel vollzogen, der zum großen Teil durch die Verbreitung von 3D-Flash angetrieben wurde. Vor der Einführung von 3D nutzten die meisten Flash-SSDs Floating-Gate-Zellen zur Datenspeicherung, doch jetzt basieren die meisten auf einer 3D-Architektur mit Charge-Trap-Zellen.

Charge Trap Flash bietet eine bessere Ausdauer und Skalierbarkeit und ist weniger anfällig für Schäden und Lecks. Außerdem verbrauchen Charge-Trap-Zellen weniger Energie und sind schneller zu programmieren.

Trotz ihrer Vorteile wurde die Umstellung auf Charge-Trap-Zellen bisher nur wenig beachtet, vielleicht auch deshalb, weil sie auch Herausforderungen mit sich bringen, insbesondere in Bezug auf die Zuverlässigkeit. Aus diesem Grund sind einige Hersteller bei Floating-Gate-Zellen geblieben und verwenden sie hauptsächlich für Planar-NAND, in begrenztem Umfang aber auch für 3D-Flash. Andere Hersteller haben stark in Charge-Trap-Technologien investiert und werden dies wahrscheinlich noch eine Weile tun.

Das Floating-Gate-Dilemma

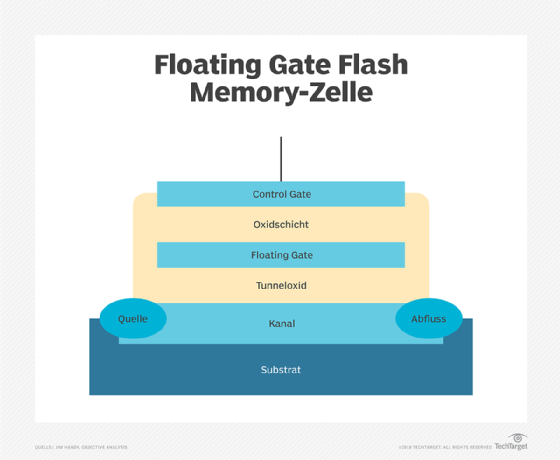

Flash-Laufwerke verwenden seit ihren Anfängen Floating-Gate-Zellen. Jede Zelle enthält ein Floating Gate, das in die Zellstruktur integriert ist. Das Floating Gate fängt Elektronen ein, wenn eine bestimmte Spannung an die Zelle angelegt wird, und gibt Elektronen frei, wenn eine andere Spannung angelegt wird.

In einem Single-Level-Cell-Laufwerk (SLC) gilt ein Floating Gate, wenn es Elektronen enthält, als geladen oder programmiert, und der Bitwert der Zelle wird als Null registriert. Andernfalls gilt die Zelle als ungeladen oder gelöscht, und ihr Bitwert wird als Eins registriert. Bei Laufwerken mit Multi-Level-Zellen (MLC), Triple-Level-Zellen (TLC) und Quad-Level-Zellen (QLC) sind die Berechnungen komplexer, aber die Grundlagen sind die gleichen.

Im Inneren der Zelle trennt eine Oxidschicht das Floating Gate vom Siliziumsubstrat, durch das die Spannung in die Zelle hinein und aus ihr heraus fließt. Die Oxidschicht ist so dünn, dass Elektronen zwischen dem Floating Gate und dem Substrat hindurchtreten können, wenn eine Spannung angelegt wird. Während eines Programmier- oder Schreibvorgangs wandern Elektronen in das Floating Gate. Während eines Löschvorgangs bewegen sich die Elektronen aus dem Floating Gate heraus.

Jeder Programm-/Löschzyklus (Program/Erase Cycle, P/E Cycle) beschädigt die Oxidschicht geringfügig, und nach einer ausreichenden Anzahl von P/E-Zyklen wird die Oxidschicht so weit erodieren, dass Elektronen aus dem Floating Gate austreten, bis es keine Ladung mehr halten kann und die Zelle unbrauchbar wird.

Da die Zellen immer kleiner und mehr Bits in jede Zelle gepackt werden, sind sie noch anfälliger für Schäden. Technologien wie Wear Leveling und Verbesserungen in der Controller-Logik haben dazu beigetragen, die Lebensdauer des Laufwerks zu verlängern, aber die Zellen werden trotzdem irgendwann ausfallen.

Die Umstellung auf 3D-Flash hat die Floating-Gate-Zelle mehr denn je vor Herausforderungen gestellt. Je größer die Anzahl der Schichten, desto schwieriger wird die Herstellung und Skalierung der Chips, zumal die Hersteller bestrebt sind, die Gesamtfläche des Chips zu verringern. Einige 3D-SSDs haben inzwischen mehr als 200 Schichten, und die Hersteller haben Pläne für noch dichtere 3D-Flash-Chips.

Floating Gate vs. Charge Trap

Aufgrund der Einschränkungen, die mit Floating-Gate-Zellen einhergehen, haben sich Flash-Hersteller wie Samsung, Micron, SK Hynix und Kioxia für den Großteil ihrer Flash-Speicher der Charge-Trap-Technologie zugewandt. Charge-Trap-Zellen gibt es schon seit einiger Zeit, aber erst als 3D-Flash aufkam, begannen die Hersteller, sie ernsthaft für SSDsder Unternehmensklasse in Betracht zu ziehen.

In vielerlei Hinsicht funktionieren Charge-Trap-Zellen ähnlich wie Floating-Gate-Zellen, wobei unterschiedliche Spannungsmuster die Elektronen in eine Auffangschicht (Trapping Layer) hinein- und herausbewegen. Es gibt jedoch einen wichtigen Unterschied. Die Floating-Gate-Zelle verwendet polykristallines Silizium, um einen Leiter für das Einfangen der Elektronen bereitzustellen. Bei der Charge-Trap-Technologie wird nichtleitendes Siliziumnitrid als Isolator verwendet.

Siliziumnitrid ist weniger anfällig für Defekte und Leckagen als polykristallines Silizium und erfordert eine geringere Spannung zur Unterstützung der P/E-Zyklen. Aus diesem Grund kann die Charge-Trap-Zelle eine dünnere Oxidschicht verwenden und die Belastung der Schicht verringern, was zu höheren Lebensdauerraten führt als bei Laufwerken mit Floating-Gate-Zellen. Der Charge-Trap-Ansatz ermöglicht außerdem schnellere Lese- und Schreibvorgänge und verbraucht weniger Energie.

Da Floating-Gate-Zellen immer kleiner werden, werden sie auch anfälliger für Störungen, zum Beispiel wenn Elektronen versehentlich von einem Floating Gate zu einem anderen fließen. Diese Störungen können zu Leistungsinkonsistenzen und fehlerhaften Daten führen. Da es sich bei der Charge-Trap-Schicht um einen Isolator handelt, sind solche Störungen unwahrscheinlicher, wodurch es möglich ist, Charge-Trap-Zellen kleiner als Floating-Gate-Zellen zu anzufertigen und infolgedessen dichtere Laufwerke mit höherer Ausdauer zu produzieren.

Herausforderungen der Charge-Trap-Technologie

So vielversprechend die Charge-Trap-Flash-Technologien auch klingen mögen, sie bringen auch Probleme mit sich. Elektronen können eingeschlossen werden, was zu einer Leistungsverschlechterung führt. Charge-Trap-Zellen können auch anfällig für Datenverluste sein, insbesondere bei höheren Temperaturen, wenn die Elektronen stärker angeregt werden, obwohl Charge-Trap-Zellen immer noch nicht so anfällig sind wie Floating-Gate-Zellen.

In seinem Artikel Recent Progress on 3D NAND Flash Technologies, der in der Fachzeitschrift Electronics veröffentlicht wurde, kann laut Akira Goda es bei Charge-Trap-Zellen auch zu Problemen mit der kurzfristigen Datenspeicherung kommen. Aufgrund des Zellendesigns ist es möglich, dass sich eine eingeschlossene Ladung entweder seitlich oder vertikal bewegt oder im Tunneloxid eingeschlossen wird, was in sehr kurzer Zeit geschehen kann.

Der Markt für Carge-Trap-Flash-Technologie

Trotz der Nachteile, die mit Charge-Trap-Zellen verbunden sind, setzen die Hersteller von 3D-Flash-Geräten auf diese Technologie. Sie unternehmen auch Schritte, um potenzielle Probleme, die mit Charge-Trap-Zellen einhergehen, zu lösen. So optimieren die Anbieter beispielsweise ihre Herstellungsprozesse, aktualisieren die Controller-Software und führen neue Designmerkmale in ihre SSDs ein.

Kioxia und Western Digital kündigten kürzlich einen 218-Layer-3D-Flash an, der ein Terabyte an Daten speichert und entweder eine TLC- oder eine QLC-Konfiguration verwendet, die beide auf Charge-Trap-Zellen basieren. Die komplementären Metall-Oxid-Halbleiter (Complementary Metal-Oxide Semiconductors, CMOS) nutzen Funktionen wie Wafer-Bonding und laterales Schrumpfen. Der Flash-Speicher enthält auch die CMOS-Technologie Direct Bonded to Array (CBA). Bei CBA werden der CMOS-Wafer und der Cell-Array-Wafer separat unter optimierten Bedingungen hergestellt und dann miteinander verbunden, was zu einer höheren Bitdichte und schnelleren I/O-Geschwindigkeiten führt.

SK Hynix geht mit seinem Charge Trap CMOS ähnlich vor. Das Unternehmen hat kürzlich einen 238-Schicht-Schaltkreis unter dem Namen 4D-Flash vorgestellt. Das 4D bezieht sich in diesem Fall auf einen Chip mit einer CMOS-Schicht über einer Peri Under Cell (PUC)-Schicht, die die periphere Logikschaltkreise enthält. Nach Angaben von SK Hynix trägt die PUC-Technologie dazu bei, die Chipgröße zu verringern und die Produktionseffizienz zu maximieren. Der Anbieter behauptet außerdem, dass seine fortschrittliche Charge-Trap-Technologie die Lese- und Schreibleistung verbessert.

Obwohl Micron bei der Einführung der Charge-Trap-Flash-Technologie langsamer war als andere Anbieter, liefert das Unternehmen jetzt einen 232-Layer-NAND-Chip aus, der diese Technologie nutzt. Der Chip basiert auf der gleichen Art von gestapeltem Ansatz wie die Chips von Kioxia, Western Digital und SK Hynix. Der Array-Wafer ist mit der Oberseite des Logik-Wafers verbunden, was Micron als CMOS under Array bezeichnet.

Samsung war einer der Pioniere der 3D-NAND- und Chare-Trap-Technologien mit seiner 2013 eingeführten Produktlinie von V-NAND-Flash-Laufwerken. Seitdem ist Samsung weltweit führend in der 3D-NAND-Branche. Samsungs aktuelle Flash-SSDs der siebten Generation umfassen 176 Schichten, aber die SSDs der achten Generation des Unternehmens sind jetzt in Produktion und werden voraussichtlich 236 Schichten aufweisen.

Die Weiterentwicklung im Storage-Bereich

Charge Trap Flash hat sich als effektive Technologie zur Verringerung der physischen Größe von SSDs erwiesen. Aus diesem Grund werden die meisten der heutigen 3D-Flash-Speicher mit Charge-Trap-Zellen gebaut. Aber auch Floating-Gate-Technologien haben sich seit längerer Zeit etabliert und werden wahrscheinlich weiterhin eine Rolle bei speicherhungrigen Anwendungen spielen, aber ihre zukünftige Rolle bei 3D-Flash ist bestenfalls ungewiss.

Flash-Laufwerke sind dichter und leistungsfähiger als je zuvor, während ihr Preis pro Gigabyte weiter sinkt. Die meisten heutigen Flash-Laufwerke basieren auf 3D-Architekturen, die Charge-Trap-Zellen verwenden und damit die Floating-Gate-Zellen als führende Technologie ablösen. Aufgrund der Verbreitung von Charge-Trap-SSDs wird es diese Technologie wahrscheinlich noch eine ganze Weile geben, und sie dürfte sich mit jeder neuen Generation weiter verbessern.